参考答案:

【问题1】 DR=低电平时,B口传向A口 【问题3】

12位

【问题2】

DR=高电平时,A口传向B口

5V÷4096÷2=0.61mv

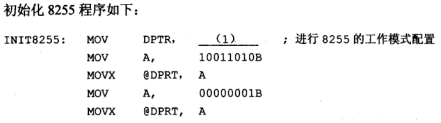

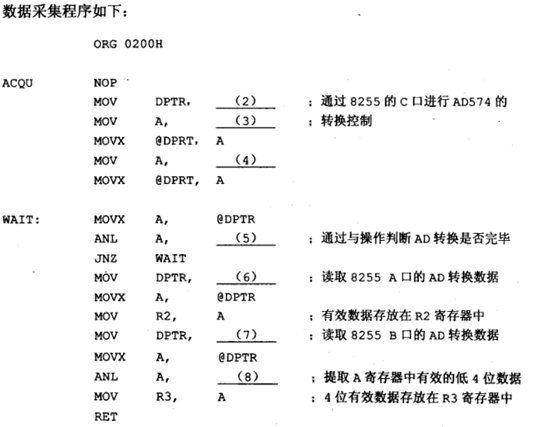

【问题4】

(1)#C003H

(2)#C002H#00H

(3)#00H

(4)#01H

(5)#80H

(6)#C000H

(7)#C001H

(8)#0FH

详细解析:

本题考查嵌入式硬件系统设计和基本的汇编程序编写知识。

【问题1】

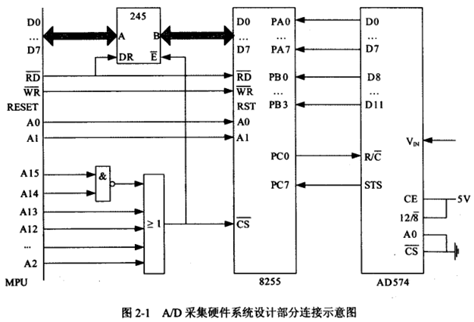

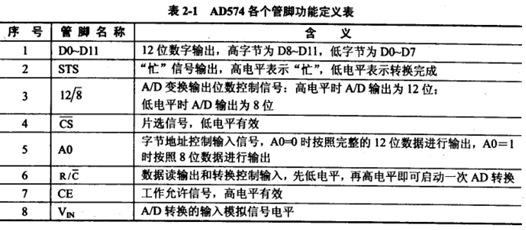

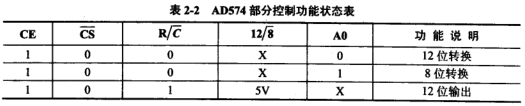

根据表 2-1中AD574各个管脚功能定义表,可以得知A0=0时按照完整的12位数据进行输出,A0=1时按照8位数据进行输出。然后从图2-1的原理图可以看出,A0接地,即低电平。所以采用的是12位转换模式。

【问题2】

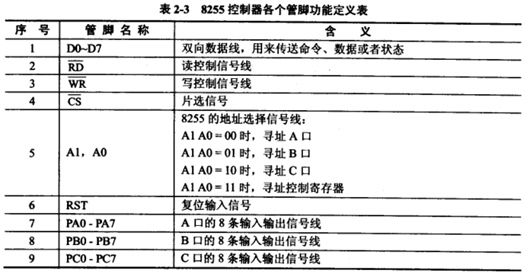

图2-1中245为双向缓冲器,在该硬件设计中配置8255控制字时,CPU需要向245进行数据输出(245的A口传输给B口);在获取AD采集数据时CPU需要接收245所 传输过来的数据(245的B口传输给A口)。根据硬件设计,根据表2-3中的RD非为读控制信号,WR非为写控制信号,都是低电平有效。而DR是跟RD非连接在一起,当DR为低电平的时候,也就是RD为低电平,所以RD是有效的,也就是读控制信号有效,是从B口传向A口。当DR为高电平的时候,RD是无效的,也就是WR为低电平有效的,也就是写控制信号有效,是从A口传向B口。

【问题3】

在该A/D变换中,如果用1/2LSB(最低有效位)来表示量化误差,当该A/D控制器的量程范围为5V时,其量化误差是5v*(1/212)*1/2=0.61mv。