参考答案:

【问题1】

(1)~(6):B、E、F、G、J、K

【问题2】

(1)A

(2)C

(3)B

(4)D

【问题3】

(1)(q->head==q->tail)&&(q->tag=0)

(2)((q->head==q->tail)&&(q->tag=1))

(3)(q->tail+1)%q->size

(4)(q->head+1)%q->size

(5)(q->head==q->tail)

(6)(q->head==(q->tail+1)%q->size))

(7)(q->tail+1)%q->size

(8)(q->head+1)%q->size

详细解析:

本题考查嵌入式系统中计算机总线、存储、环形队列等相关知识。

【问题1】

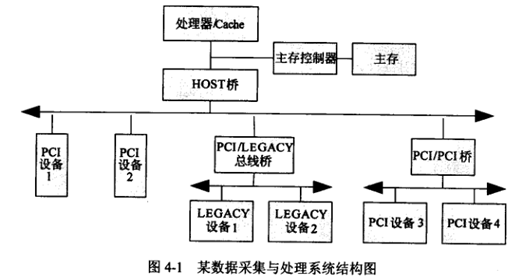

该方案是基于PCI总线的多功能处理系统。PCI(Peripheral Component Interconnect)总线是一种高性能局部总线,是为了满足外设间以及外设与主机间高速数据传输而提出来的。在数字图形、图像和语音处理,以及高速实时数据采集与处理等对数据传输率要求较高的应用中,采用PCI总线来进行数据传输,可以解决原有的标准总线数据传输率低带来的瓶颈问题。

PCI总线是一种树型结构,并且独立于CPU,可以和CPU并行操作。PCI总线上可以挂接PCI设备和PCI桥片,一个PCI设备可以既是主设备也是从设备,但是在同一个时刻,这个PCI设备或者为主设备或者为从设备。在PCI总线中有3类设备,PCI主设备、PCI从设备和桥设备。其中PCI从设备只能被动地接收来自HOST主桥,或者其他PCI设备的读写请求;而PCI主设备可以通过总线仲裁获得PCI总线的使用权,主动地向其他PCI设备或者主存储器发起存储器读写请求。而桥设备的主要作用是管理下游的PCI总线,并转发上下游总线之间的总线事务。PCI总线有3种桥,即HOST/PCI桥、PCI/PCI桥和PCI/LEGACY 桥。

PCI总线的地址总线与数据总线是分时复用的。这样做的好处是,一方面可以节省接插件的管脚数,另一方面便于实现猝发数据传输。在做数据传输时,由一个PCI设备做发起者(主控,Initiator或Master),而另一个PCI设备做目标(从设备,Target或Slave)。总线上的所有时序的产生与控制,都由Master来发起。PCI总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构(Arbiter),来决定谁有权力拿到总线的主控权。

PCI总线有如下显著的特点:

(1)高速性,PCI局部总线以33MHz的时钟频率操作,采用32位数据总线,数据传输速率可高达132MB/S,远超过以往各种总线。而早在1995年6月推出的PCI总线规范2.1已定义了64位、66MHz的PCI总线标准。因此PCI总线完全可为未来的计算机提供更高的数据传送率。另外,PCI总线的主设备(Master)可与计算机内存直接交换数据,而不必经过计算机CPU中转,也提高了数据传送的效率。

(2)即插即用性,PCI设备识别主要是对开发商代码和设备代码进行识别,PCI设备的硬件资源,则是由计算机根据其各自的要求统一分配,绝不会有任何的冲突问题。作为PCI板卡的设计者,不必关心计算机的哪些资源可用,哪些资源不可用,也不必关心板卡之间是否会有冲突。

(3)可靠性,PCI独立于处理器的结构,形成一种独特的中间缓冲器设计方式,将中央处理器子系统与外围设备分开。这样用户可以随意增添外围设备,以扩充计算机系统而不必担心在不同时钟频率下会导致性能的下降。PCI总线增加了奇偶校验错(PERR)、系统错(SERR)、从设备结束(STOP)等控制信号及超时处理等可靠性措施,使数据传输的可靠性大为增加。

(4)复杂性,PCI总线强大的功能大大增加了硬件设计和软件开发的实现难度。硬件上要采用大容量、高速度的CPLD或FPGA芯片来实现PCI总线复杂的功能。软件上则要根据所用的操作系统,用软件工具编制支持即插即用功能的设备驱动程序。

(5)自动配置,PCI总线规范规定PCI设备可以自动配置。PCI定义了3种地址空间:存储器空间、输入/输出空间和配置空间,每个PCI设备中都有256字节的配置空间用来存放自动配置信息,在系统初始化时,通过idsel引脚片选决定PCI设备,自动根据读到的有关设备的信息,结合系统的实际情况为设备分配存储地址、中断和某些定时信息。

(6)共享中断,PCI总线是采用低电平有效方式,多个中断可以共享一条中断线。

(7)扩展性好,如果需要把许多设备连接到PCI总线上,而总线驱动能力不足时,可以采用多级PCI总线,这些总线上均可以并发工作,每个总线上均可挂接若干设备。因此PCI总线结构的扩展性是非常好的。

(8)多路复用,在PCI总线中为了优化设计采用了地址线和数据线共用一组物理线路,即多路复用。PCI接插件尺寸小,又采用了多路复用技术,减少了元件和管脚个数,提高了效率。

(9)严格规范,PCI总线对协议、时序、电气性能、机械性能等指标都有严格的规定,保证了PCI的可靠性和兼容性。由于PCI总线规范十分复杂,其接口的实现就有较高的技术难度。

【问题2】

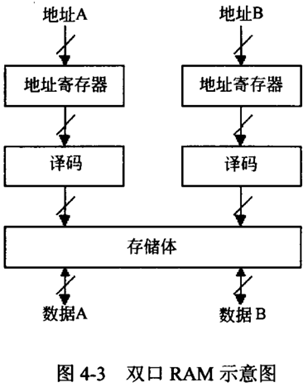

双口RAM是在一个存储器上具有两套完全独立的数据线、地址线和读写控制线,并允许两个独立的系统同时对该存储器进行随机性的访问。每个读写口都有一套自己的地址寄存器和译码电路,可以并行地独立工作。两个读写口可以按各自接收的地址同时读出或写入,或一个写入而另一个读出。与两个独立的存储器不同,两个读写口的访存空间相同,可以访问同一个存储单元。通常使双端口存储器的一个读写口面向CPU,另一个读写口则面向外设或输入/输出处理机。如图4-3所示。

双口RAM最大的特点是存储数据共享。一个存储器配备两套独立的地址、数据和控制线,允许两个独立的CPU或控制器同时异步地访问存储单元。因为数据共享,就必须存在访问仲裁控制。当两个端口对同一内存操作时,当两个端口同时对同一地址单元读出数据,或者两个端口不同时对同一地址单元存取数据的情况下,两个端口的存取不会出现错误;当两个端口同时对同一地址单元写入数据的情况下,会出现写入错误;当两个端口同时对同一地址单元,一个写入数据,另一个读出数据的情况下,会出现读出错误。

【问题3】

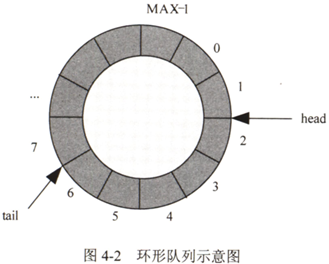

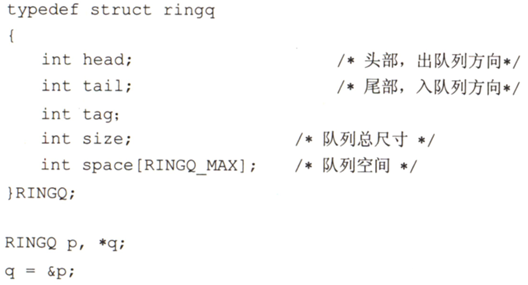

环形队列是在实际编程极为有用的数据结构,它有如下特点:它是一个首尾相连的FIFO的数据结构,采用数组的线性空间;数据组织简单,能很快知道队列是否满或空;能以很快的速度来存取数据。因为简单高效,甚至在硬件都实现了环形队列。

内存上没有环形的结构,因此环形队列实际上是数组的线性空间来实现。那当数据到了尾部如何处理呢?它将转回到0位置来处理。这个转回是通过数组下标索引取模操作(Index% MAXN)来实现的。

因此环列队列的是逻辑上将数组元素q[0]与q[MAXN-l]连接,形成一个存放队列的环形空间。为了方便读写,还要用数组下标来指明队列的读写位置。定义Head/tail两个变量,其中head指向可以读的位置,tail指向可以写的位置。

环形队列的关键是判断队列为空,还是为满。当tail追上head时,队列为满;当head追上tail时,队列为空。但如何知道谁追上谁,还需要一些辅助的手段来判断。

如何判断环形队列为空、为满有两种判断方法。一是附加一个标志位tag,当head赶上tail,队列空,则令tag=0,当tail赶上head,队列满,则令tag=l;二是限制tail赶上head,即队尾结点与队首结点之间至少留有一个元素的空间。队列空时head==tail,队列满时(tail+1)%MAXN==head。

入队操作时,如队列不满,则写入9->1311=(9->tail+1)%q->size;出队操作时,如果队列不空,则从head处读出。下一个可读的位置在q->head=(q->head+1)%q->size。