参考答案:

【问题1】

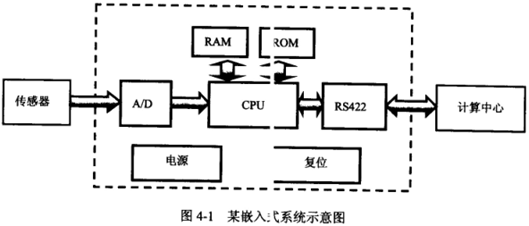

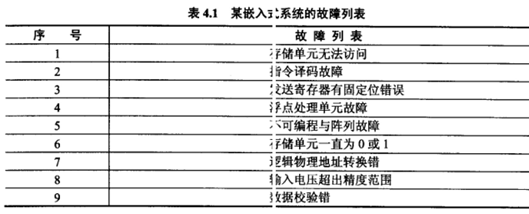

CPU故障:2,4,7

RAM故障:1,6,9

【问题2】

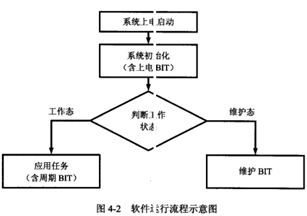

(1)周期BIT

(2)维护BIT

(3)上电BIT

【问题3】

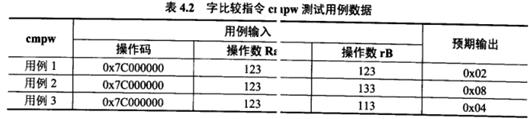

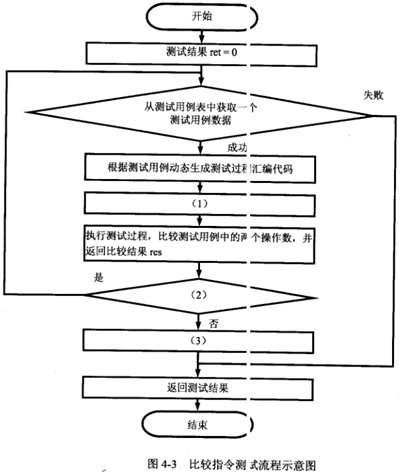

(1)刷新指令Cache(高速缓存)

(2)将res与测试用例表中的预期结果进行比较

(3)测试结果ret=1

详细解析:

测试模式设计常用的BIT包括:上电自检(IBIT)、周期自检(CBIT)、启动BIT和维修自检(MBIT)。

IBIT用于任务前,CBIT用于任务中MBIT用于离线状态。这三种BIT针同一系统的不同阶段,以提高故障检测和隔离能力:

(1)IBIT:系统上电后立即开始,通常只运行一次,以保证系统在提供安全功能前是完好的;同时还可以验证系统正常运行时无法验证的重要设备的故障,比如部分故障隔离装置等。

(2)CBIT:系统正常运行器件的测试,以保证系统在运行过程中故障即使被检测出;可为针对持续的状态量的检测,也可以为周期性的功能性检测,安全评估的重要对象。

(3)启动BIT在系统运行过程中,由操作人员启动运行,检测设备中可能存在的故障。

(4)MBIT:系统离线状态下的测试,以改善系统的可维修性和安全性,也可用来覆盖在线自检无法覆盖的故障模式检测。